# *Lecture* **0\_3.1**

Semiconductor Technology trends

#### **Paolo PRINETTO**

Politecnico di Torino (Italy) Univ. of Illinois at Chicago, IL (USA) CINI Cybersecurity Nat. Lab. (Italy)

Paolo.Prinetto@polito.it

www.consorzio-cini.it www.comitato-girotondo.org **License Information**

# This work is licensed under the Creative Commons BY-NC License

To view a copy of the license, visit: http://creativecommons.org/licenses/by-nc/3.0/legalcode

Lecture 0\_3.1 - Slide 2

Rel. 03.03.2019

© Prinetto - 2019

## **Disclaimer**

- We disclaim any warranties or representations as to the accuracy or completeness of this material.

- Materials are provided "as is" without warranty of any kind, either express or implied, including without limitation, warranties of merchantability, fitness for a particular purpose, and noninfringement.

- Under no circumstances shall we be liable for any loss, damage, liability or expense incurred or suffered which is claimed to have resulted from use of this material.

Goal

This lecture aims at presenting the current trends in the microelectronic industries, with peculiar emphasis on some recent developments, such as SoC, SiP, 3D packaging, and NoC.

# **Prerequisites**

#### - None

Lecture 0\_3.1 - Slide 5

## Homework

- Students are warmly invited to visit:

- . web pages related to microelectronic trends

- . web pages of the Intel site related to the Moore's law:

- www.intel.com/technology/mooreslaw/inde x.htm

- . web pages on 3D technology advances:

- www.youtube.com/watch?v=WiTustspfA&feature=em-uploademail

# Further readings

The International Technology Roadmap for Semiconductors home page at

http://public.itrs.net

# Further readings

- Students interested in making a reference to a text book on the arguments covered in this lecture can refer, for instance, to:

- G. Conte, A. Mazzeo,

N. Mazzocca, P. Prinetto:

"Architettura dei

calcolatori",

Città Studi, 2015

(App. C Evoluzione

Tecnologica)

(In Italian)

Architettura dei calcolatori

CittoStudi

# Outline

Moore's law

– Advances in components:

. System-on-Chip (SoC)

. IP-cores

- Advances in architectures:

. MPSoC

– Advances in packaging:

. Advances in Device packaging

. Advances in System packaging

– Advances in on-chip communications:

. Network-on-Chip (NoC)

Lecture 0\_3.1 - Slide 9

# Outline

#### – Moore's law

– Advances in components: . System-on-Chip (SoC) . IP-cores - Advances in architectures: . MPSoC - Advances in packaging: . Advances in Device packaging . Advances in System packaging - Advances in on-chip communications:

. Network-on-Chip (NoC)

Lecture 0\_3.1 - Slide 11

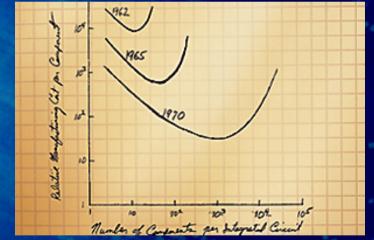

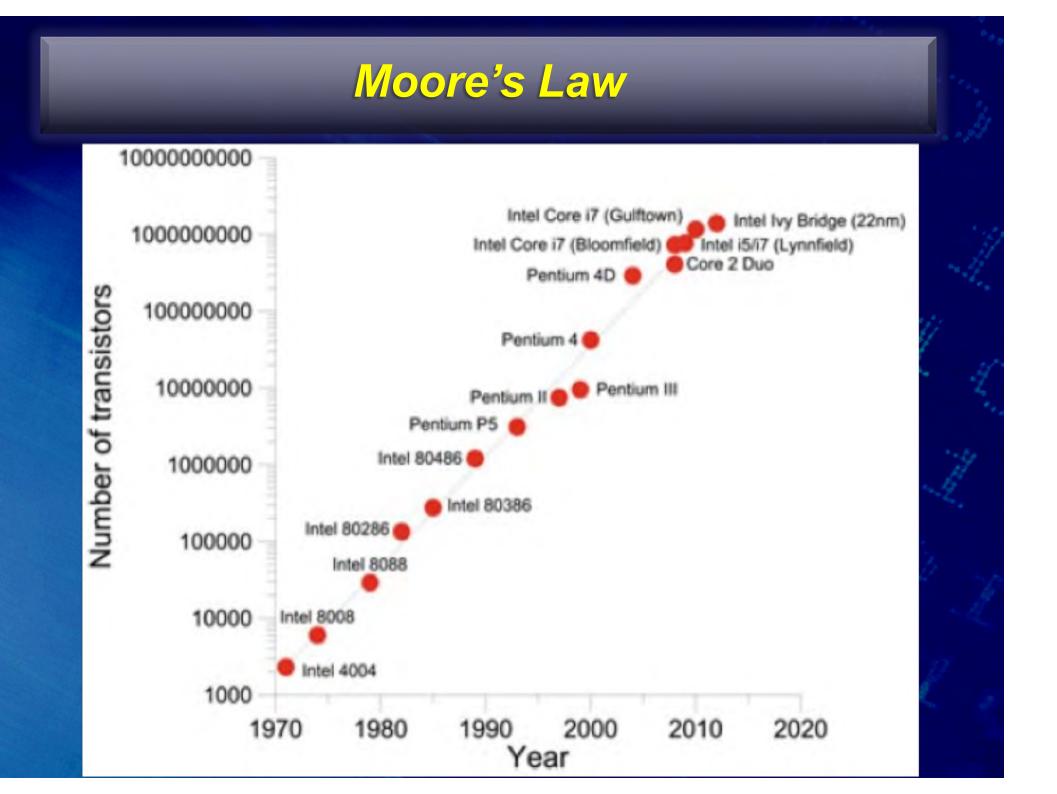

# Moore's law

## Processor transistor counts doubles every two years

Gordon Moore's original graph from 1965

http://www.intel.com/technology/mooreslaw/index.htm

Lecture 0\_3.1 - Slide 12

Rel. 03.03.2019

© Prinetto - 2019

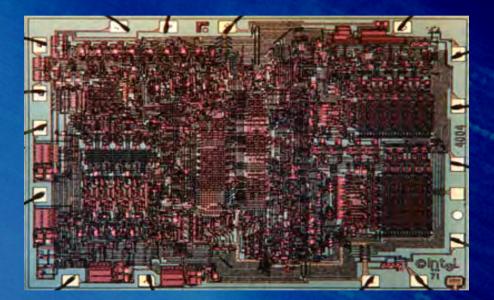

### Intel 4004 (1971)

#### 2.3 k transistors

#### **1.8 G transistors**

X 780,000

Lecture 0\_3.1 - Slide 14

Rel. 03.03.2019

© Prinetto - 2019

# Outline

#### – Moore's law

– Advances in components:

- . System-on-Chip (SoC)

- . IP-cores

- Advances in architectures:

- . MPSoC

- Advances in packaging:

- . Advances in Device packaging

- . Advances in System packaging

- Advances in on-chip communications:

- . Network-on-Chip (NoC)

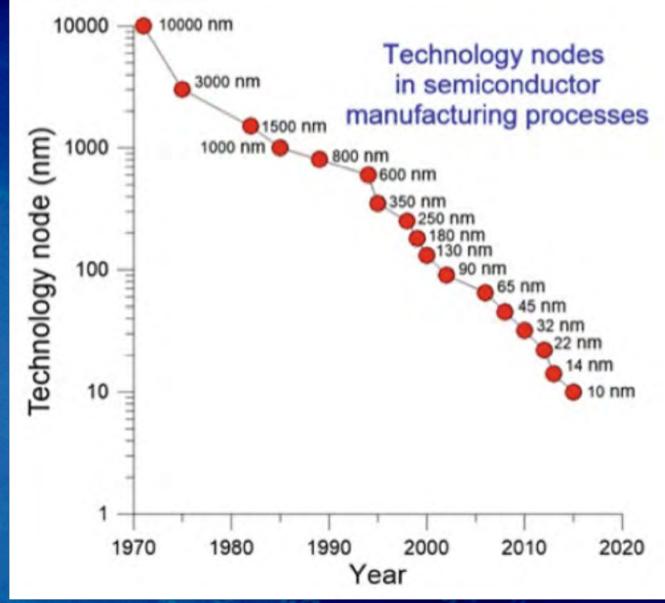

# Semiconductor Technology Nodes

Lecture 0\_3.1 - Slide 16

Rel. 03.03.2019

© Prinetto - 2019

# Technology node

The technology node is traditionally defined as the first layer metal half-pitch or the gate length in the fabrication process

> Actual Gate Length

Polysilicon Gate Electrode

Effective Gate Length

Drawn gate length L<sub>drawn</sub> Actual gate length L<sub>actual</sub> Effective gate length L<sub>effective</sub> Effective gate length L<sub>effective</sub>

- ~ Width specified by layout engineer

- ~ Actual physical width of gate material

- ~ Over etch shortens physical width of gate

- $\sim$  Dopant migration shortens effective gate length

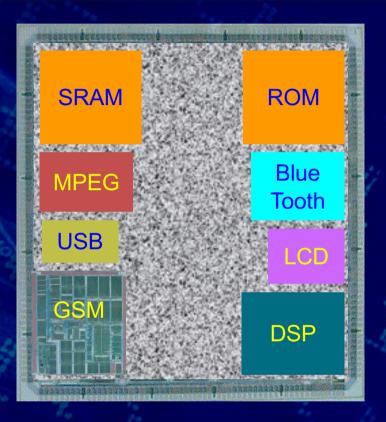

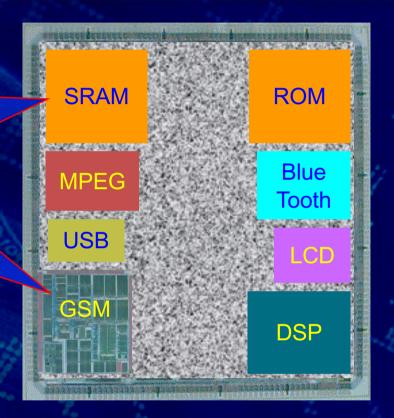

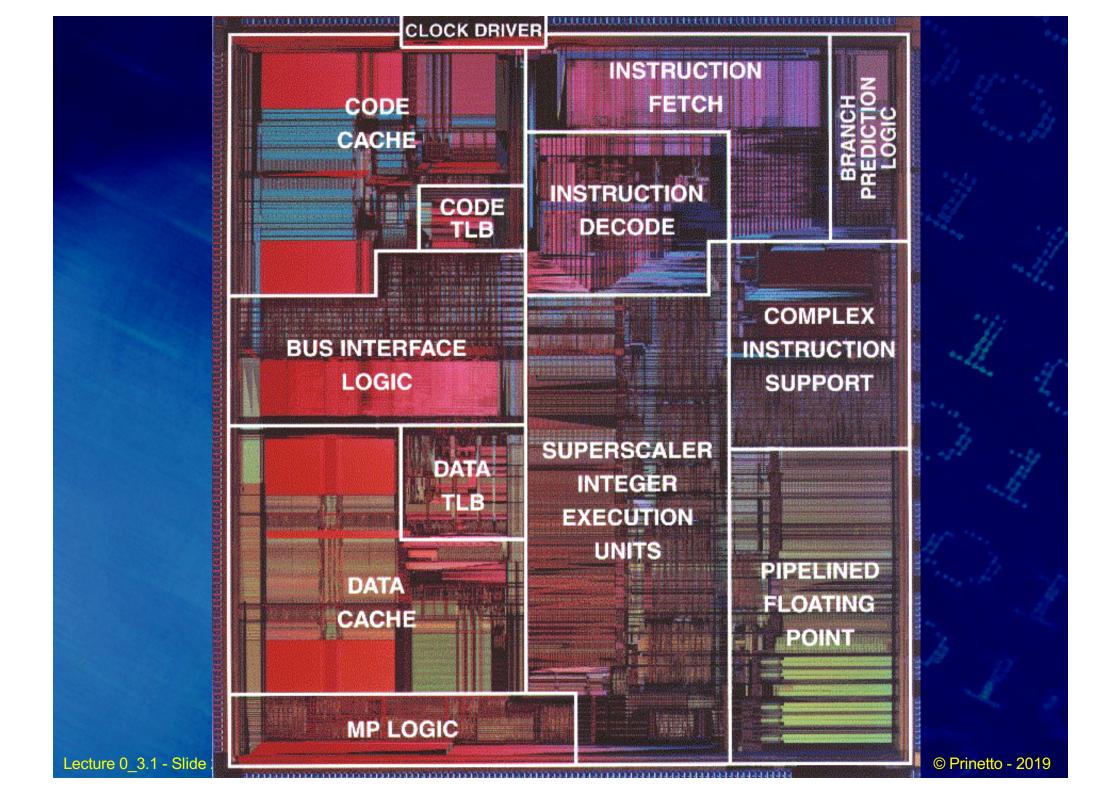

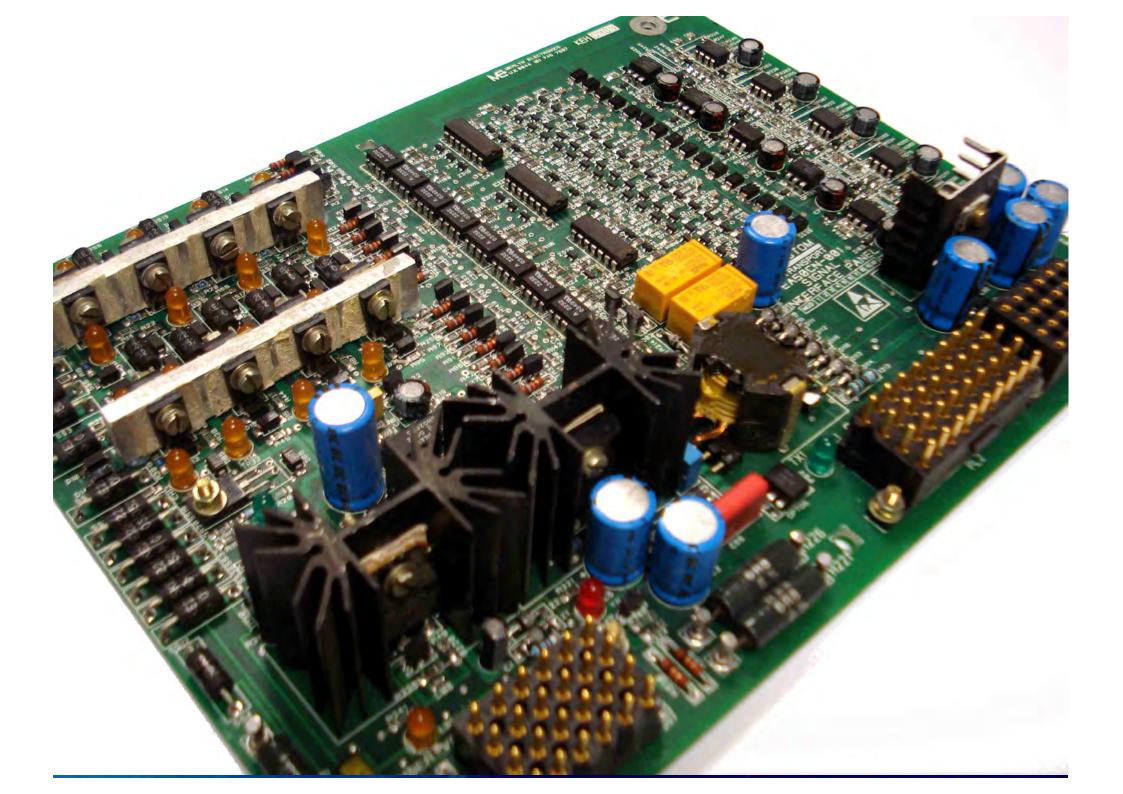

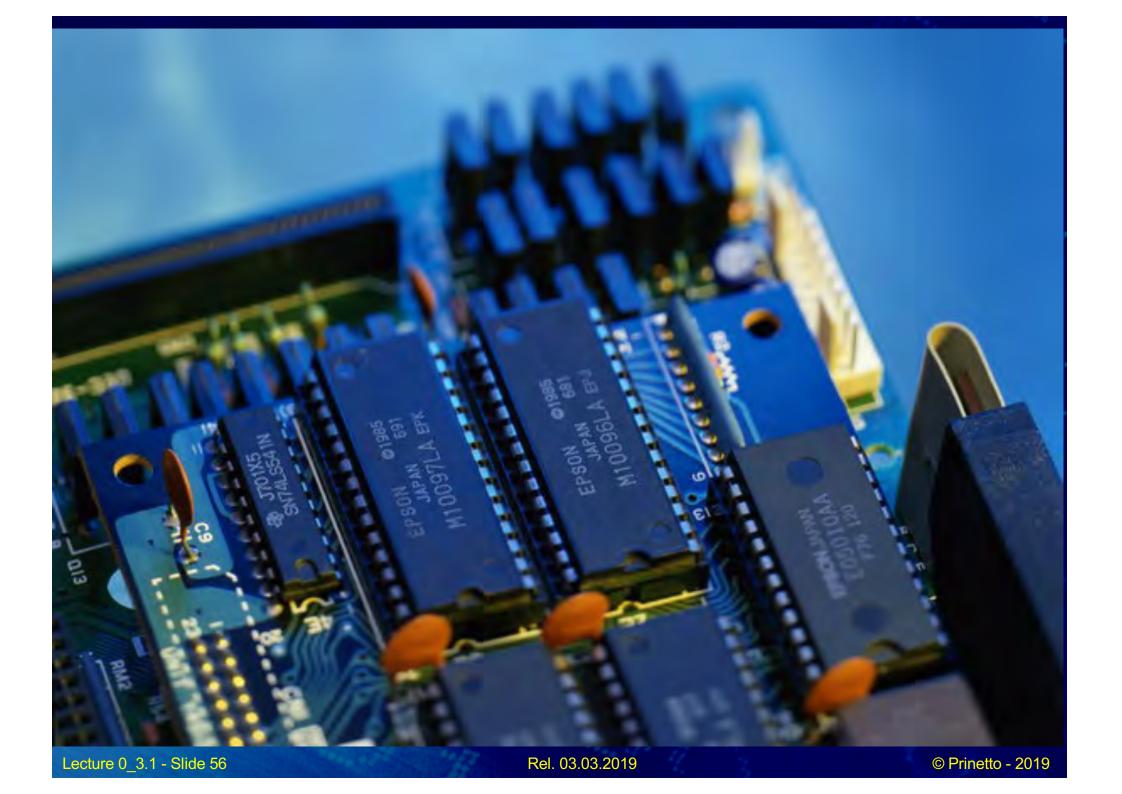

Yesterday's PCBs (System-on-aboard)

# SoC trends

Yesterday's PCBs (System-on-aboard)

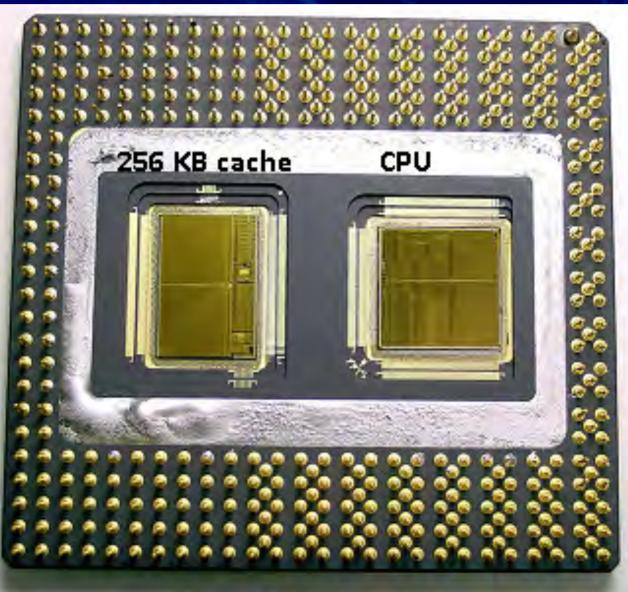

Today's chips (System-on-a-chip)

# SoC trends

Yesterday's PCBs (System-on-aboard)

Today's chips (System-on-a-chip)

Tomorrow's re-usable IP-cores

# IP core

A hardware circuit design implementing a well-defined set of functions that is lent, sold, or licensed from one provider to a customer

# An example

## An example

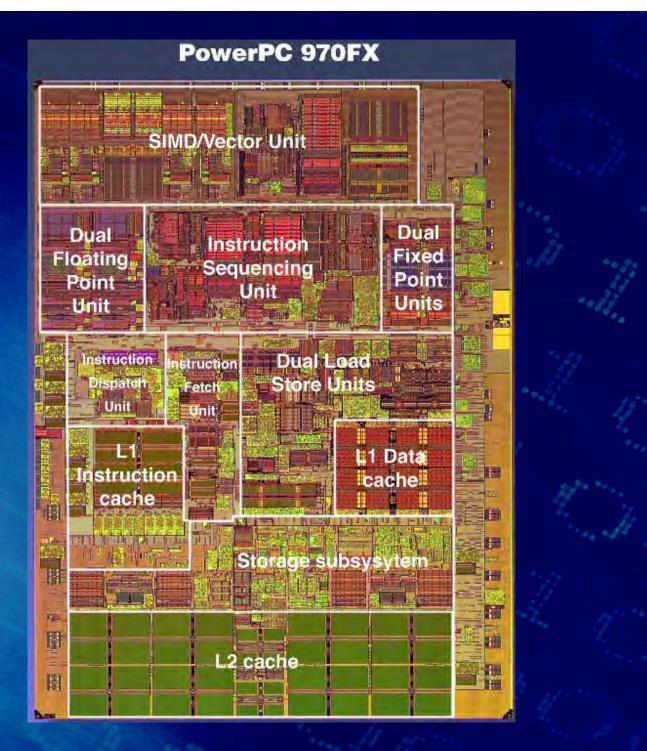

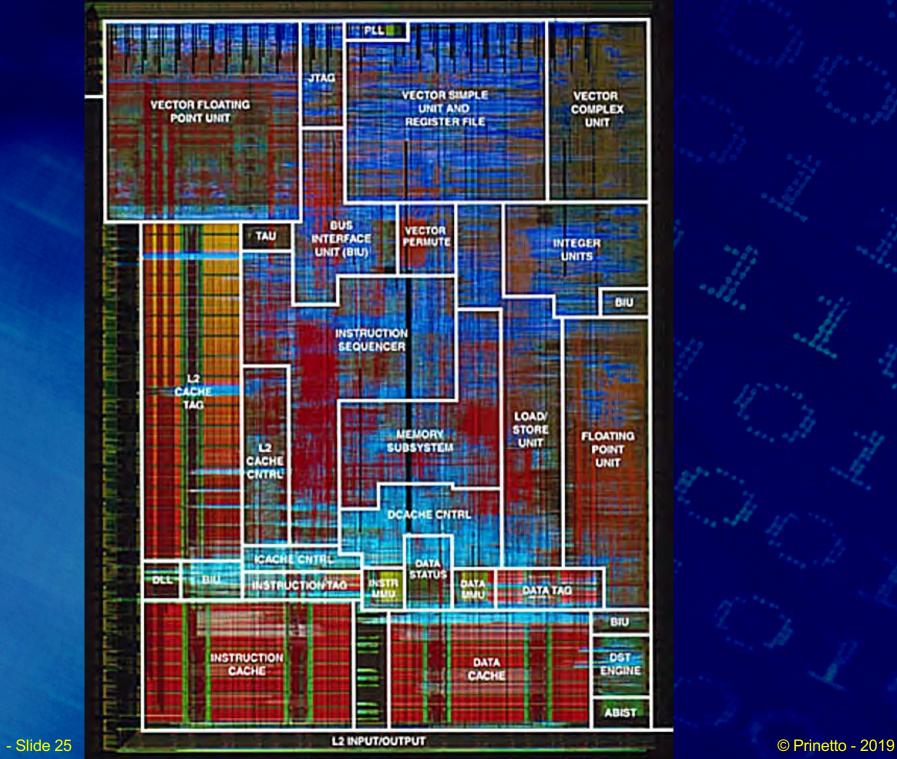

Embedded Cores: Pre-designed, pre-verified functional blocks, also termed IP (Intellectual Property), or macro.

Lecture 0\_3.1 - Slide 24

Lecture 0\_3.1 - Slide 25

# High costs for design

The design cost for SoC at 28 nm counted up to 80 - 100 M US \$

due to increasing NRE costs

- Total SoC design costs increased 89% from the 28nm node to the 14nm node and are expected to increase 32% again at the 10nm node and 45% at the 7nm node.

- Total Software design costs increased 74% at the 28nm node and are forecast to show a CAGR of 69% through the 7nm node

- 14nm silicon with a \$20.00 ASP is required to ship 9.954M units to reach the breakeven point.

# High costs for production

# High costs for production

14 nm production line

Lectu

## 10+ Billions !!!

Rel. 03.03.2019

© Prinetto - 2019

## 36% of fabs & 45% of production capacity are in high risk areas

3.03.2019

© Prinetto - 2019

## **Risks**

### Just 4 silicon companies:

- Samsung

- Intel

- TMSC (Taiwan)

- Global Foundries (UAE)

# Outline

Moore's law

– Advances in components:

. System-on-Chip (SoC)

. IP-cores

– Advances in architectures:

- . MPSoC

- Advances in packaging:

. Advances in Device packaging

. Advances in System packaging

– Advances in on-chip communications:

. Network-on-Chip (NoC)

# Intel's Tick-Tock Model of chip making

## The "Tick-Toc" Evolution to Intel® 6th Generation

## **Pollack's Rule**

In a given process technology, performance increase is roughly proportional to square root of increase in complexity

## **Pollack's Rule**

In a given process technology, performance increase is roughly proportional to square root of increase in complexity

> In other words, if you double the logic in a processor core, then it delivers only 40% more performance

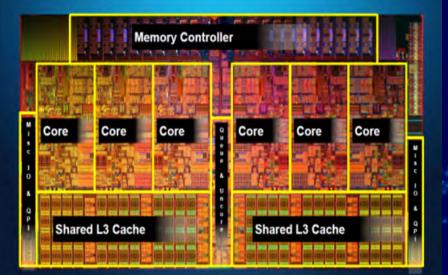

## Consequences: MPSoC MultiProcessor SoC Architecture

They provide near linear performance improvement with complexity and power

## Consequences: MPSoC MultiProcessor SoC Architecture

They provide near linear performance improvement with complexity and power

> Two smaller processor cores, instead of a large monolithic processor core, can potentially provide 70-80% more performance, as compared to only 40% from a large monolithic core

## Applying Pollack's rule inversely...

- Performance of a smaller core reduces as squareroot of the size, but power reduction is linear, resulting in smaller performance degradation with much larger power reduction

- Overall, the compute throughput of the system increases linearly with the larger number of small cores.

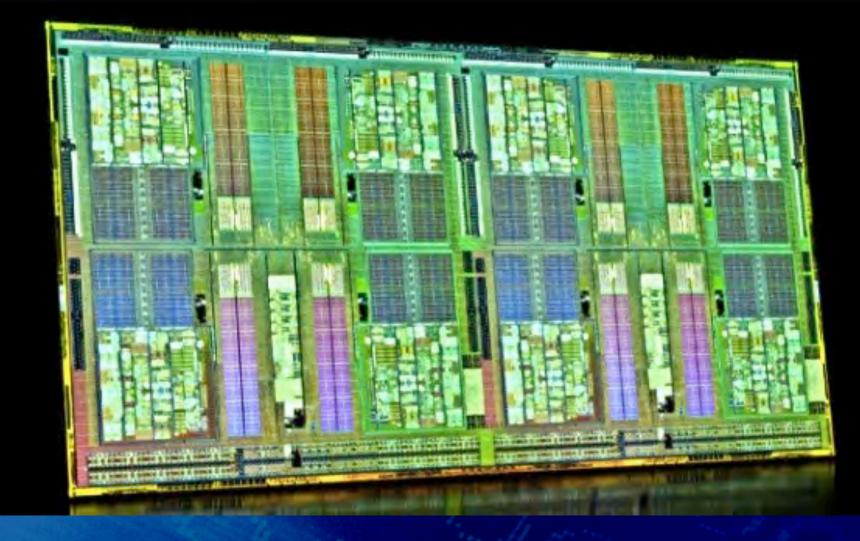

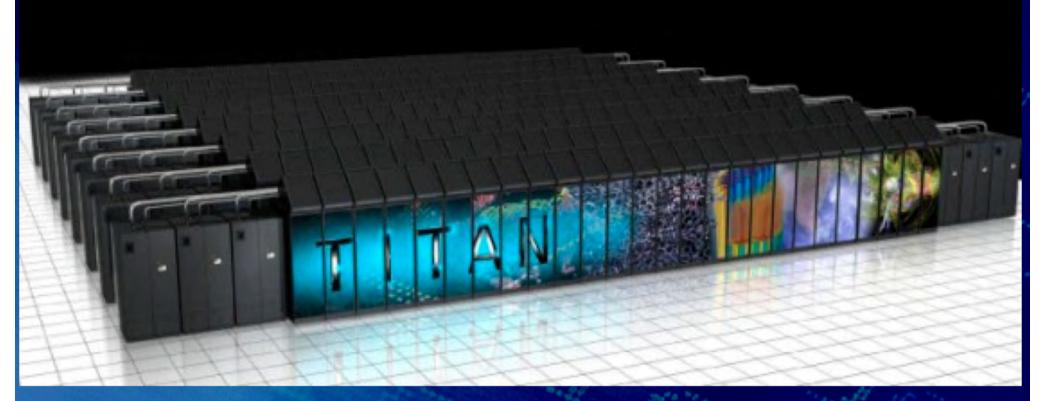

# **CPU AMD Opteron** including 16 cores x86 at 2.6 GHz

- 17.59 PFlop/s (10<sup>15</sup> Flop/s)

- 18,688 CPU AMD Opteron + 18,688 CGPU Nvidia Tesla, for a total of 560,640 processor core

- Consumes 8.2 MW

- Total memory of 700 TB

## Multiprocessors additional benefits

- Each processor core can be individually turned on or off, thereby saving power

- Each processor core can be run at its own optimized supply voltage and frequency

- Easier to load balance among processor cores to distribute heat across the die

- Can potentially produce lower die temperatures improving reliability and leakage

## Outline

Moore's law

Advances in components:

System-on-Chip (SoC)

IP-cores

Advances in architectures:

- . MPSoC

- Advances in packaging:

. Advances in Device packaging

. Advances in System packaging

– Advances in on-chip communications:

. Network-on-Chip (NoC)

Rel. 03.03.2019

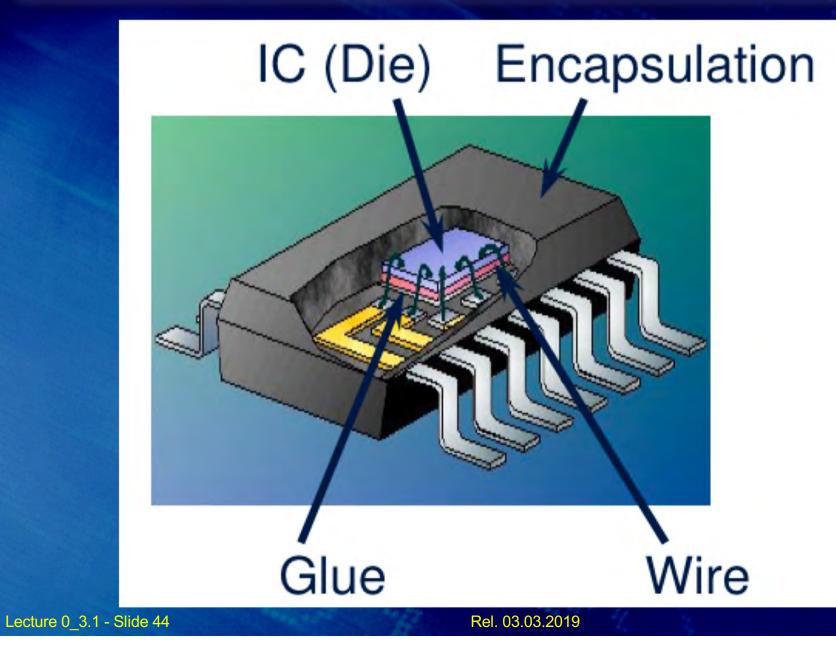

## IC's traditional package

# Advances in Device Packaging

## Advances in Device Packaging

### PTH (Pin Through Hole) device

# **PTH components**

### PTH (Pin Through Hole) component

## **PTH components**

#### **Multi-layer PCB**

Up to 12 layers

Lecture 0\_3.1 - Slide 48

Rel. 03.03.2019

## Advances in Device Packaging

### PTH (Pin Through Hole) device

## SMD (Surface Mounted Device)

Lecture 0\_3.1 - Slide 49

Rel. 03.03.2019

## Surface Mount Device

# **SMD (Surface Mounted Device)** component

## Advances in Device Packaging

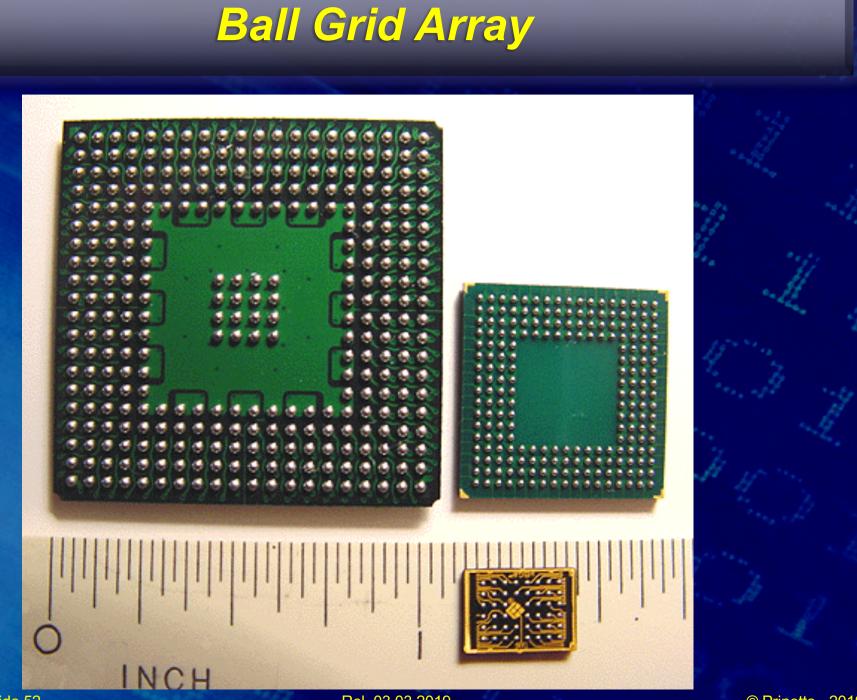

## BGA (Ball Grid Array) device

#### PTH (Pin Through Hole) device

SMD (Surface Mounted Device)

Lecture 0\_3.1 - Slide 51

Rel. 03.03.2019

Lecture 0\_3.1 - Slide 52

Rel. 03.03.2019

## Outline

Moore's law - Advances in components: . System-on-Chip (SoC) . IP-cores - Advances in architectures: . MPSoC - Advances in packaging: . Advances in Device packaging . Advances in System packaging - Advances in on-chip communications: . Network-on-Chip (NoC)

Lecture 0\_3.1 - Slide 53

Rel. 03.03.2019

# Advances in System Packaging

PCB (Printed Circuit Board)

Rel. 03.03.2019

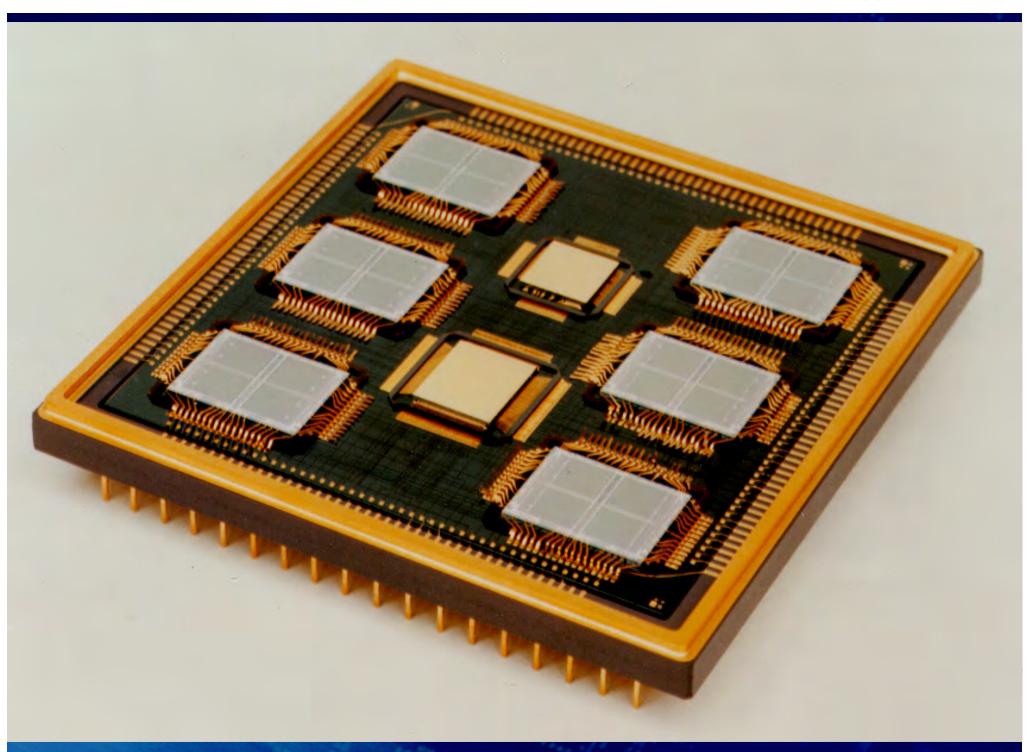

# Advances in System Packaging

MCM (Multi-Chip Modules)

Lecture 0\_3.1 - Slide 57

Rel. 03.03.2019

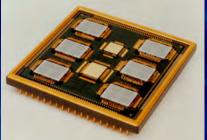

## Multi Chip Modules (MCM)

multi-layer ceramic

Lecture 0\_3.1 - Slide 58

Rel. 03.03.2019

Lecture 0\_3.1 - Slide 59

#### PCB (Printed Circuit Board)

MCM (Multi-Chip Modules)

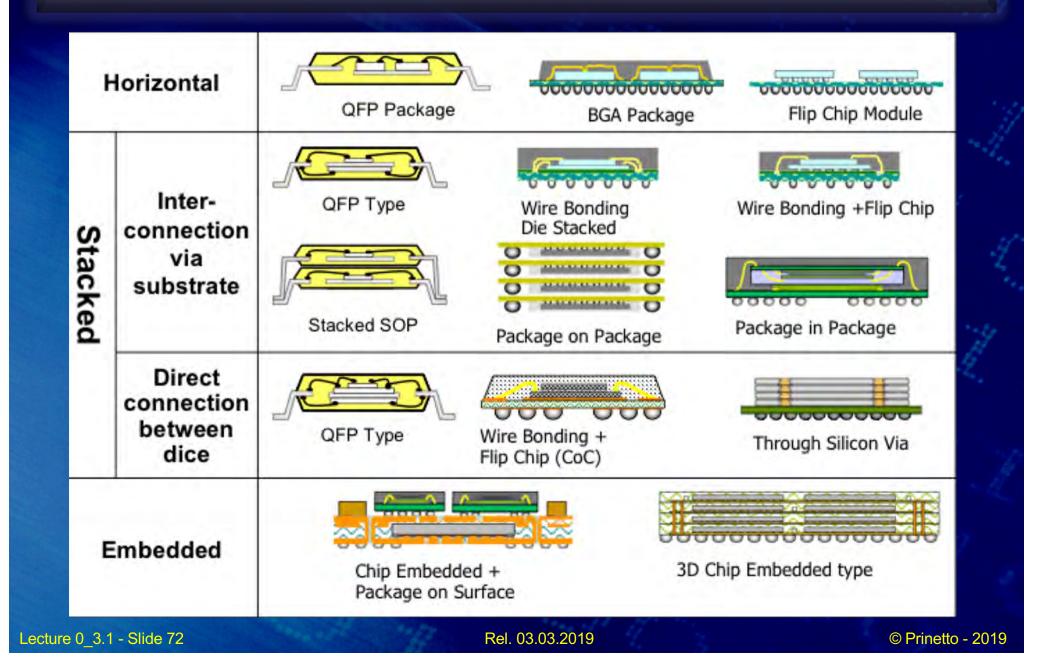

# Advances in System Packaging

#### SiP (System-in-

Package)

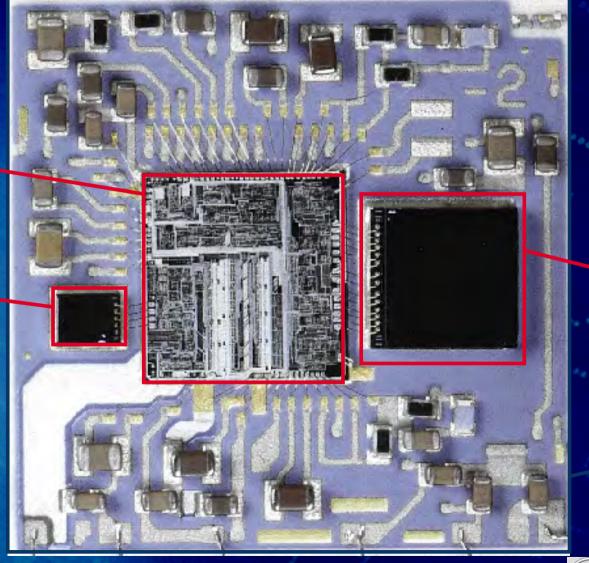

## System-inpackage (SiP)

A combination of multiple active electronic components of different functionality, assembled in a single unit that provides multiple functions associated with a system or sub-system

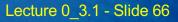

## System-in-Package (SiP)

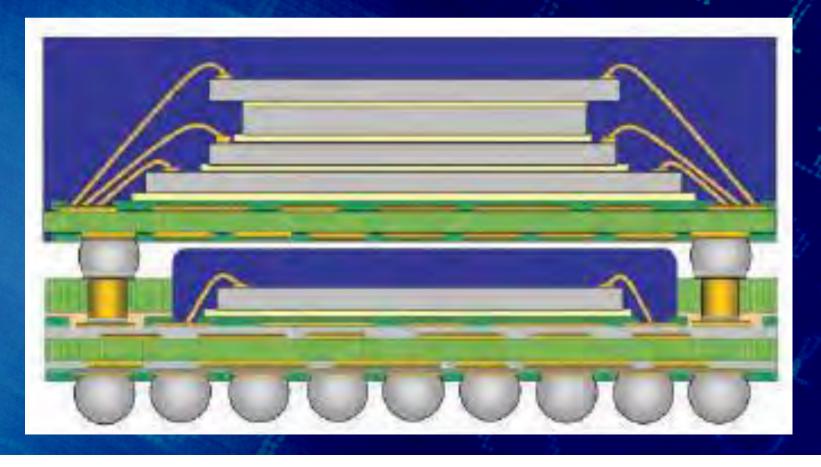

- contains more than 1 silicon die

- utilizes a substrate or carrier

- can include passive, sensors, actuators, MEMS, bio-chips, ...

- works as a "functional block" or as a "sub-system"

- comes in various packaging technologies

#### SiP Packaging Technologies

Side-by-side

#### Flip Chip / Wire bond

#### Stacked / Wire bond

Lecture 0\_3.1 - Slide 64

1.01.00.00.2010

ASIC (Signal Processing, Bus Control)

Micromechanical Acceleration Sensor

Micromech. Yaw Rate Sensor

Micro hybrid Carrier

#### PCB (Printed Circuit Board)

MCM (Multi-Chip Modules)

# Advances in System Packaging

## SiP

(System-in-Package)

3-D IC

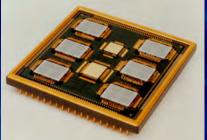

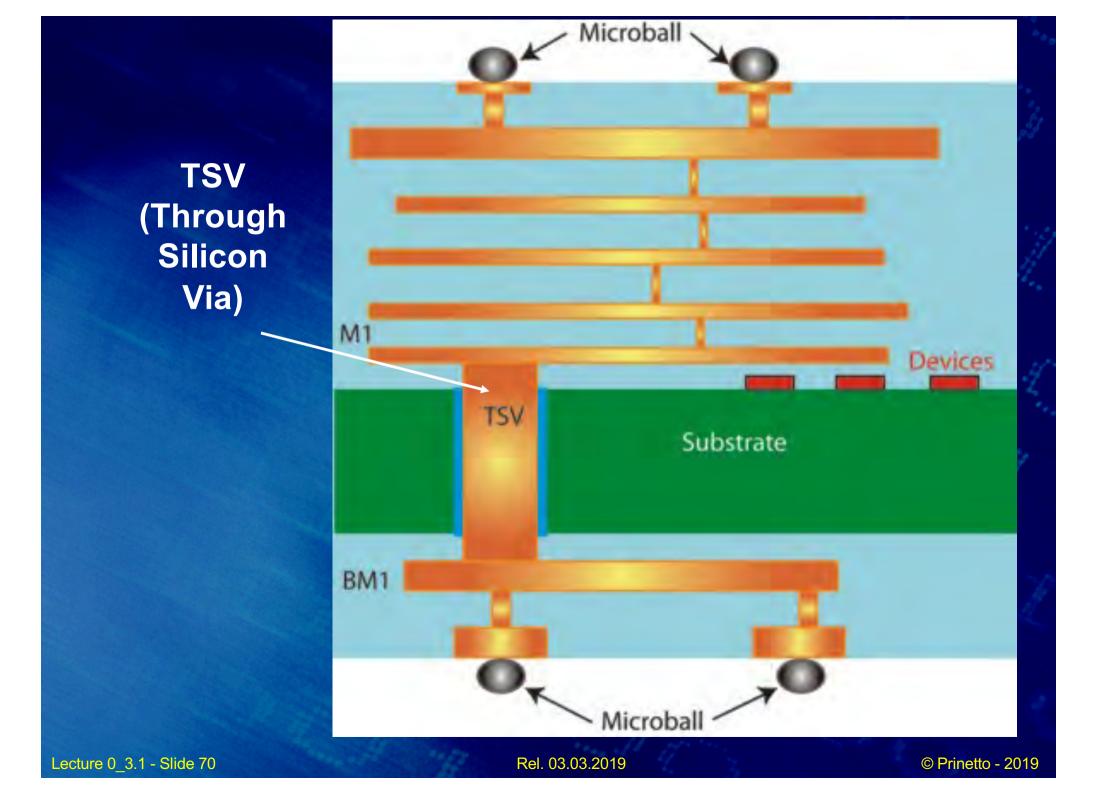

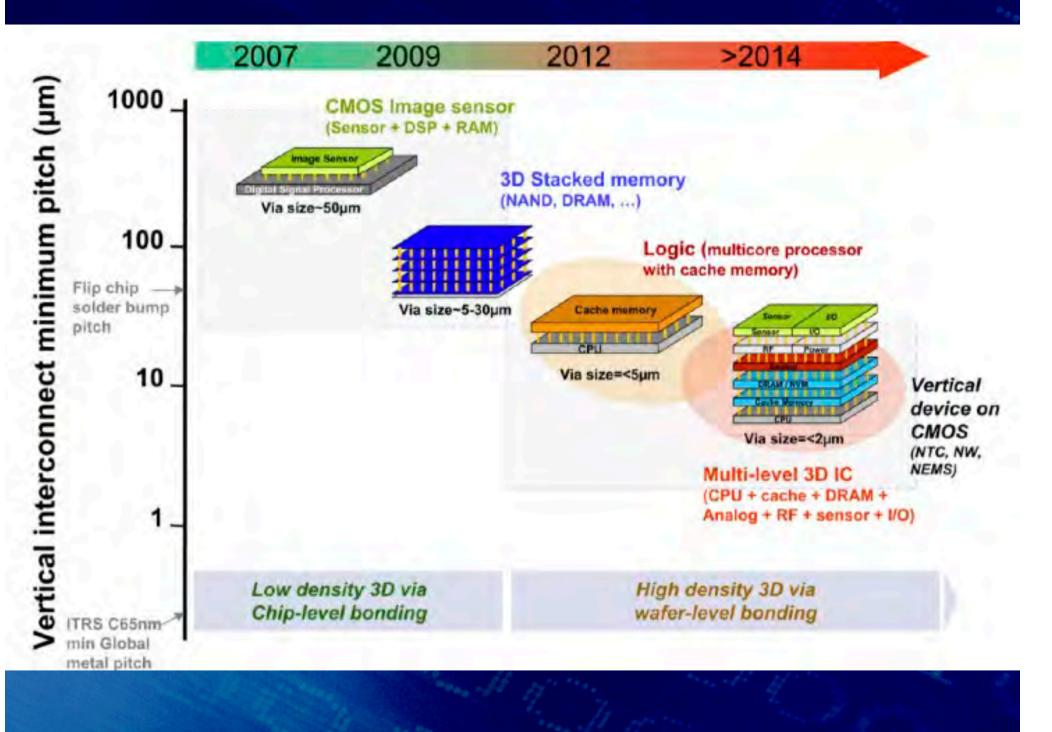

## **3-D IC Packaging**

3-D IC Packaging is a general concept that simply means the assembly of parts in a vertical direction (typically by stacking)

Lecture 0\_3.1 - Slide 71

Rel. 03.03.2019

## **SiP Categories**

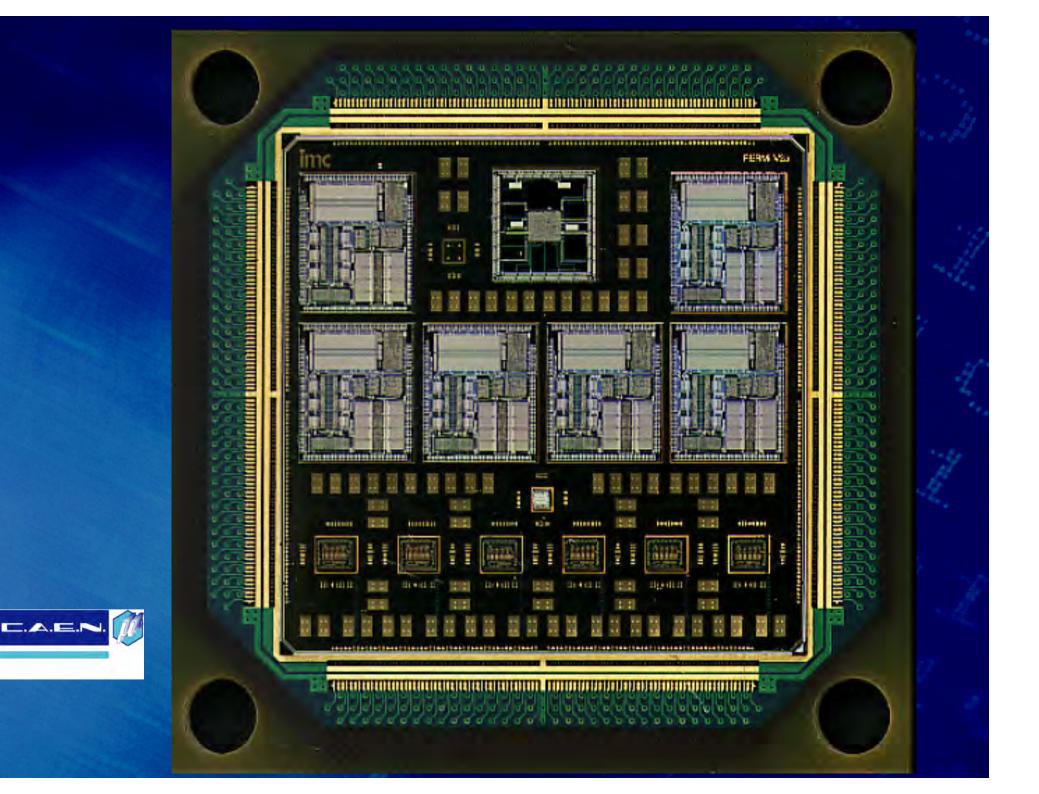

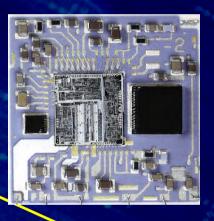

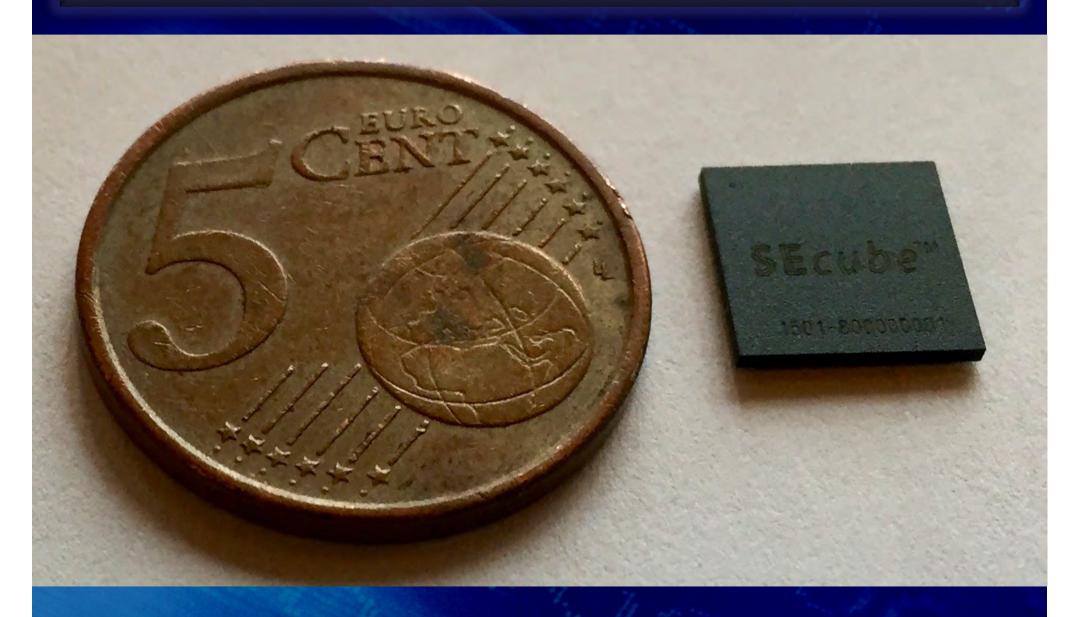

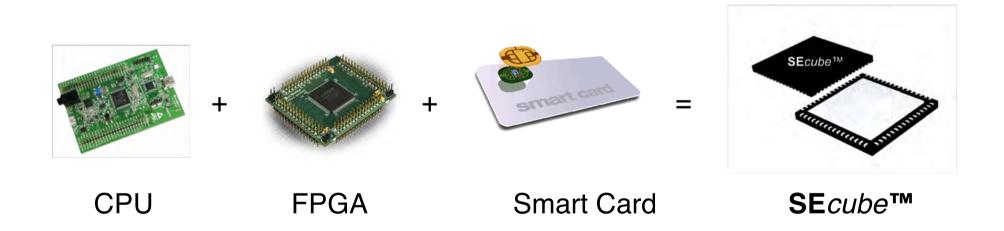

# SEcube: a real SiP example

# SEcube: a real SiP example USE cube USE cube USE cube USE cube **USE** mini • . 8 10

Lecture 0\_3.1 - Slide 74

Rel. 03.03.2019

© Prinetto - 2019

#### SEcube<sup>™</sup> - Single Chip Open Security Platform

The first Open Security Platform in a Single Chip:

- ✓ ARM Cortex M4, Floating Point, Low Power CPU

- FPGA for Hardware Custom Developments

- Security Controller (Smart Card) certified EAL 6+ (SW EAL 5+)

#### Outline

Moore's law

– Advances in components:

. System-on-Chip (SoC)

. IP-cores

– Advances in architectures:

. MPSoC

– Advances in packaging:

. Advances in Device packaging

. Advances in System packaging

- Advances in on-chip communications:

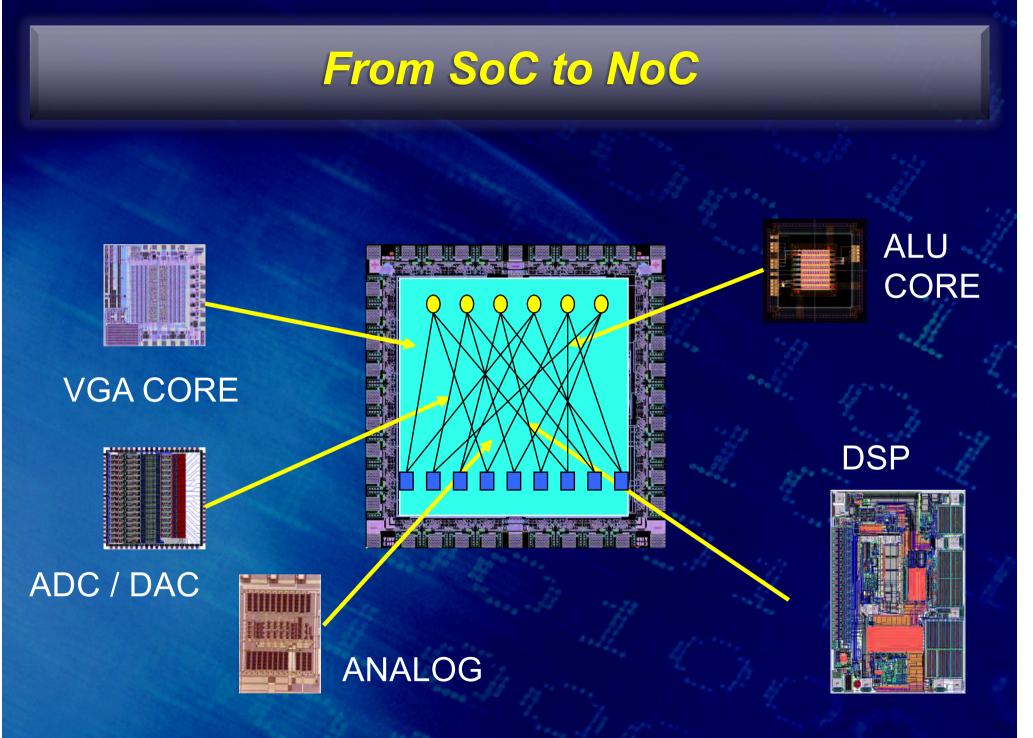

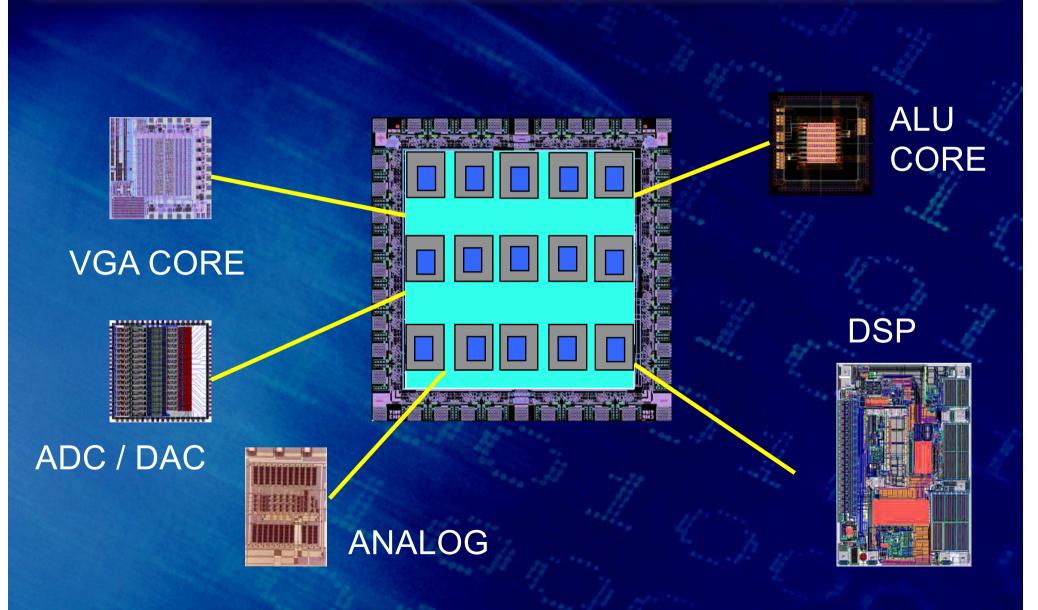

. Network-on-Chip (NoC)

Lecture 0\_3.1 - Slide 76

Rel. 03.03.2019

Lecture 0\_3.1 - Slide 77

Rel. 03.03.2019

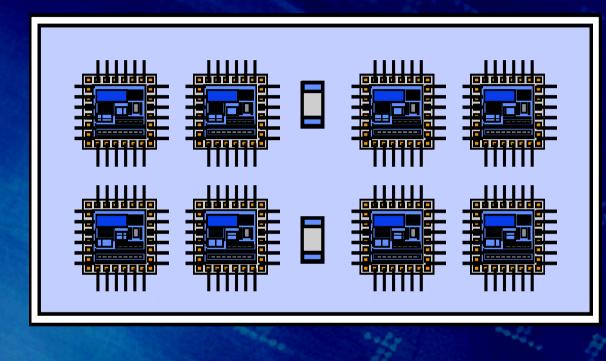

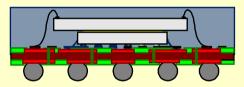

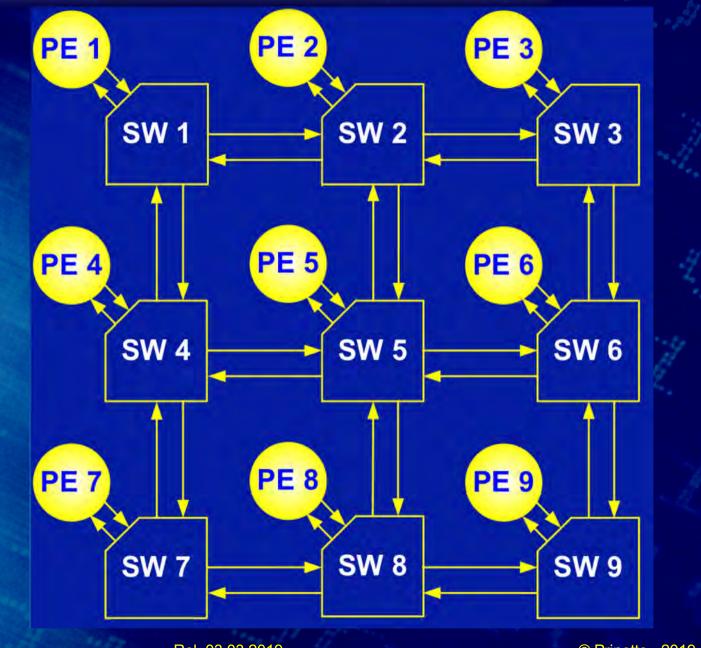

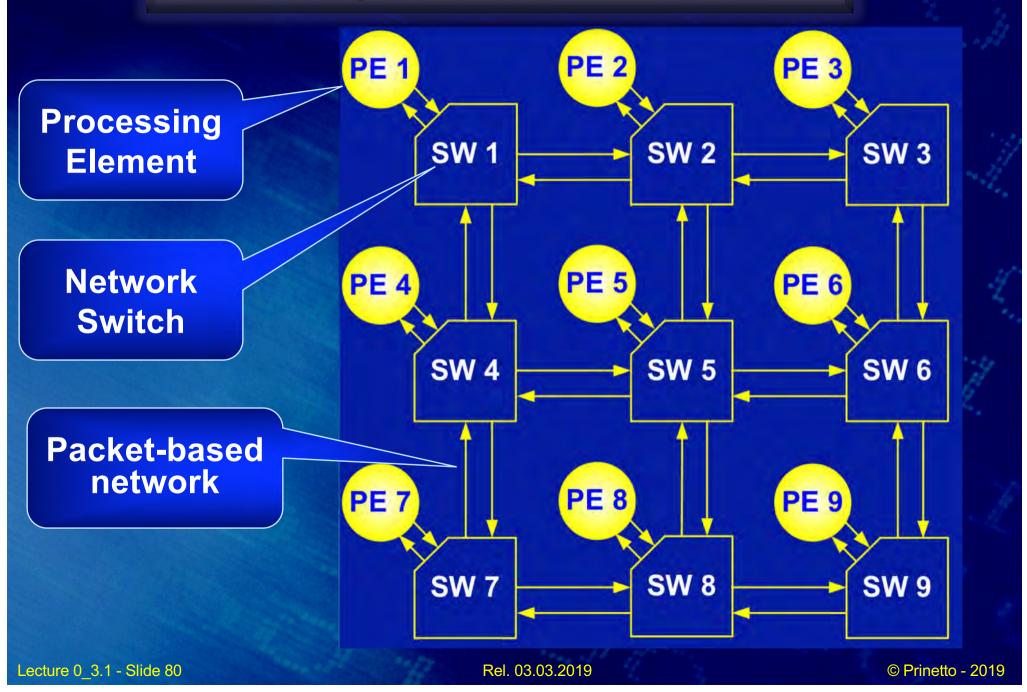

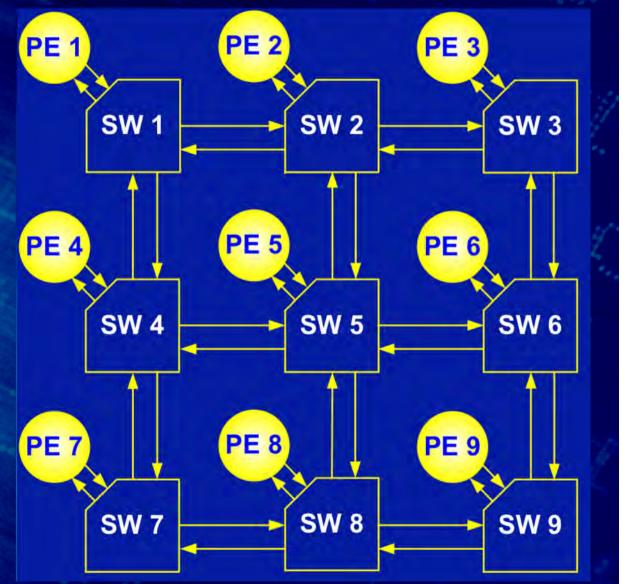

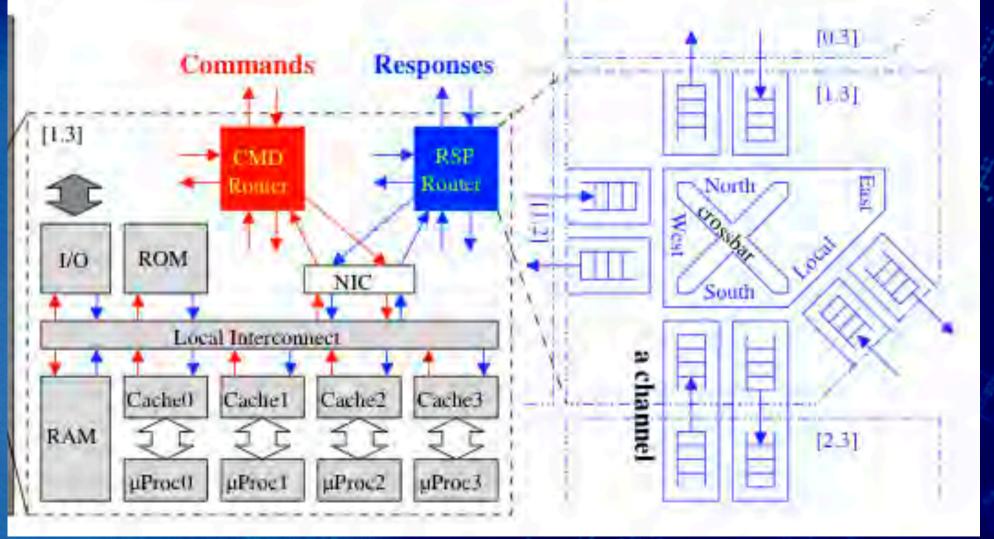

### An example of 3 x 3 mesh NoC

Lecture 0\_3.1 - Slide 79

Rel. 03.03.2019

© Prinetto - 2019

### An example of 3 x 3 mesh NoC

#### Network-On-Chip (NoC)

- Processing Elements (PEs) interconnected via packet-based network

- Processing Elements can be any type of computation unit

- Messages packetized and routed to destinations where they are depacketized into data

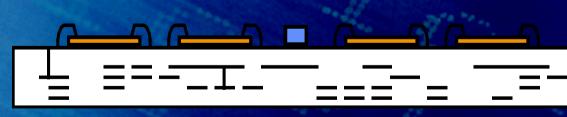

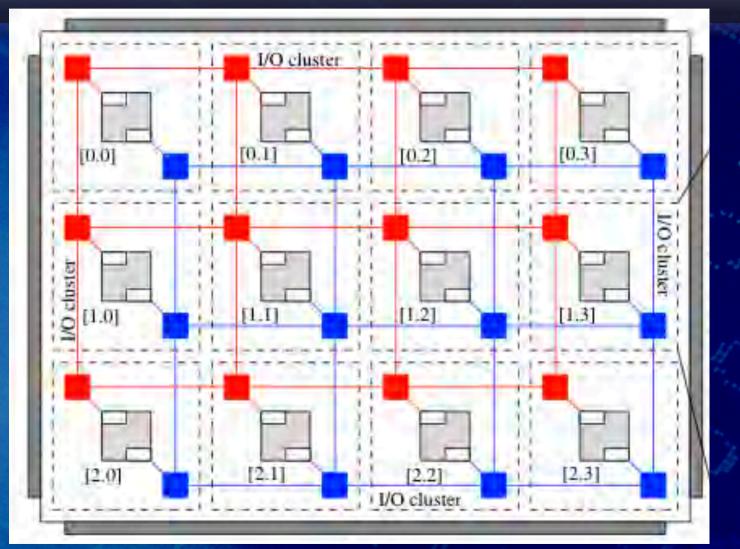

# An NoC based Massively Parallel Multi-Processor System-on-Chips (MP2SoCs) architecture

[University Pierre et Marie Curie, LIP6-SoC Laboratory, Paris, France]

# An NoC based Massively Parallel Multi-Processor System-on-Chips (MP2SoCs) architecture

[University Pierre et Marie Curie, LIP6-SoC Laboratory, Paris, France]